# Low-Voltage Back-Gated Atmospheric **Pressure Chemical Vapor Deposition Based Graphene-Striped Channel** Transistor with High- $\kappa$ Dielectric **Showing Room-Temperature** Mobility > 11 000 cm<sup>2</sup>/V $\cdot$ s

## Casey Smith,<sup>†,\*</sup> Ramy Qaisi,<sup>†</sup> Zhihong Liu,<sup>‡</sup> Qingkai Yu,<sup>‡</sup> and Muhammad Mustafa Hussain<sup>†,\*</sup>

<sup>†</sup>Integrated Nanotechnology Lab, Electrical Engineering Program, Computer Electrical Mathematical Science and Engineering Division, King Abdullah University of Science and Technology, Thuwal 23955-6900, Saudi Arabia and <sup>‡</sup>Ingram School of Engineering, Texas State University, San Marcos, Texas, United States

**ABSTRACT** Utilization of graphene may help realize innovative low-power replacements for III-V materials based high electron mobility transistors while extending operational frequencies closer to the THz regime for superior wireless communications, imaging, and other novel applications. Device architectures explored to date suffer a fundamental performance roadblock due to lack of compatible deposition techniques for nanometer-scale dielectrics required to efficiently modulate graphene transconductance  $(q_m)$

while maintaining low gate capacitance-voltage product ( $C_{as}V_{as}$ ). Here we show integration of a scaled (10 nm) high- $\kappa$  gate dielectric aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) with an atmospheric pressure chemical vapor deposition (APCVD)-derived graphene channel composed of multiple 0.25 µm stripes to repeatedly realize room-temperature mobility of 11 000 cm<sup>2</sup>/V·s or higher. This high performance is attributed to the APCVD graphene growth quality, excellent interfacial properties of the gate dielectric, conductivity enhancement in the graphene stripes due to low tox/Wgraphene ratio, and scaled high-K dielectric gate modulation of carrier density allowing full actuation of the device with only  $\pm 1$  V applied bias. The superior drive current and conductance at  $V_{dd}$  = 1 V compared to other top-gated devices requiring undesirable seed (such as aluminum and poly vinyl alcohol)-assisted dielectric deposition, bottom gate devices requiring excessive gate voltage for actuation, or monolithic (nonstriped) channels suggest that this facile transistor structure provides critical insight toward future device design and process integration to maximize CVD-based graphene transistor performance.

**KEYWORDS:** graphene  $\cdot$  striped channel  $\cdot$  back-gate  $\cdot$  high- $\kappa \cdot Al_2O_3 \cdot$  mobility

raphene, a two-dimensional allotrope of sp<sup>2</sup>-bonded carbon, has generated tremendous interest across many disciplines of scientific research due to its unique electronic, mechanical, thermal, and chemical properties.<sup>1</sup> Room-temperature carrier mobility as high as 10000 cm<sup>2</sup>/V·s, small but controllable band gap, and very high cutoff frequency are some of the electronic properties of graphene that make it one of the key enabling materials for realizing low-power RF devices.<sup>2-5</sup> Many groups have previously reported on the performance of back-gated

field effect transistors (FET) utilizing graphene synthesized by various techniques including exfoliation of highly ordered pyrolitic graphite, chemical vapor deposition, epitaxial growth on silicon carbide, and reduction of graphitic oxide.<sup>6-9</sup> The vast majority of back-gated transistor devices utilize thick (330 nm) silicon dioxide (SiO<sub>2</sub>) as both isolation and gate dielectric to facilitate optical detection of the graphene channel albeit at the expense of very high switching voltage.<sup>10</sup> Attempts have been made to tailor the thickness of higher dielectric constant materials such as silicon

\* Address correspondence to casev.smith@kaust.edu.sa: muhammadmustafa.hussain@kaust.edu.sa.

Received for review February 16, 2013 and accepted June 18, 2013.

Published online June 18, 2013 10 1021/nn400796h

© 2013 American Chemical Society

VOL.7 • NO.7 • 5818-5823 • 2013

nitride  $(Si_3N_4)$  or aluminum oxide  $(Al_2O_3)$  that still preserve the optical signature of graphene to improve electrostatic coupling.<sup>11–15</sup> Unfortunately, even the reduced thickness of these materials still requires high switching voltage because the dielectric thickness required for optical detection is at least an order of magnitude too large for low-power devices with reasonable gain  $(q_m/q_{ds})$ . In this work, we have demonstrated room-temperature mobility that is very high and at low-voltage operation by overcoming two important barriers to study graphene interaction with scaled high- $\kappa$  dielectrics: (i) the difficulty of dielectric deposition on hydrophobic (untreated/pristine) graphene and (ii) lack of optical signature for graphene transferred to scaled high- $\kappa$  dielectrics. The key to achieving this study is fabrication of back-gated devices on heavily doped silicon wafers where atomic layer deposition (ALD) was used to deposit scaled gate dielectric aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) prior to aqueousbased transfer of continuous, uniform, and wafer-sized high-quality graphene synthesized by atmospheric pressure chemical vapor deposition (APCVD) such that the need for precise alignment of discrete source/ drain contacts is eliminated (Figure 1). A comparable demonstration can be found in Han et al.'s work.<sup>16</sup> It is critically important to note that the graphene/ dielectric interfacial quality is not impacted by the use of metal or polymer seed layers to facilitate growth of ALD high-k dielectrics on hydrophobic graphene sheets, and transfer of our large ( $\sim$ 6 cm  $\times$  6 cm) graphene sheets that cover the majority of the wafer surface circumvents the need for optical detection during subsequent lithography steps, whereas seeing the graphene is a requirement for randomly placed noncontinuous films.

### **RESULTS AND DISCUSSION**

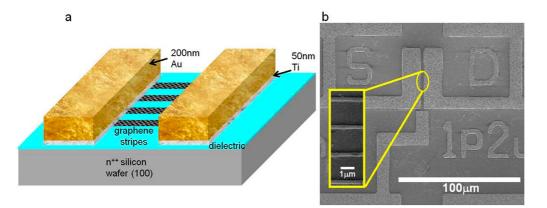

The Raman spectra shown in Figure 2 possess an  $I_{2D}$ /  $I_{\rm G}$  ratio of 2–3 depending upon the substrate with little or no evidence of D peak signature (from graphene on Cu foil and  $Al_2O_3$ ), thereby confirming the high quality of the double-layer graphene synthesized for use in this study. Moreover, the Raman map indicates a fairly uniform normalized  $I_{2D}/I_G$  peak intensity ratio over a large 40  $\mu$ m  $\times$  40  $\mu$ m area, while the accompanying optical image (of graphene on SiO<sub>2</sub>) shows isolated higher contrast spots where the graphene sheet has wrinkled or folded during PMMA transfer from the Cu foil substrate. The dilute methane used during synthesis has been shown to suppress homogeneous nucleation density of graphene on copper foil and results in very large single-domain regions of graphene.<sup>17–19</sup> We expect that the majority of our device channels will easily fit within a single graphene domain, thereby reducing carrier scattering mechanisms at graphene grain boundaries and therefore affording higher mobility. The general broadening and appearance of satellite peaks near the conventional 1585  $cm^{-1}$  G band in the specimens on  $SiO_2$  and thin  $Al_2O_3$  substrates are expected due to interaction with the substrate.20,21

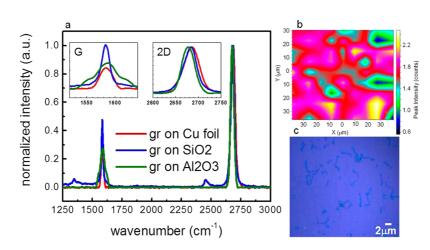

Transfer characteristics normalized for both channel width and gate overdrive of representative devices with gate length of  $L_q = 2.4 \ \mu m$  on SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> substrates are shown in Figure 3a. Both devices exhibit p-type conduction typically seen in CVD-derived graphene films transferred from the growth substrate to the insulating substrate in aqueous solution media.<sup>22</sup> The device with scaled high- $\kappa$  Al<sub>2</sub>O<sub>3</sub> dielectric and striped graphene channel has an ION/IOFF ratio of 3.75 and nearly  $3000 \times$  higher normalized peak linear transconductance  $(g_m)$  than the SiO<sub>2</sub> specimen. These characteristics are rarely seen in back-gated devices and are attributed to the high quality of the graphene channel material, nonseeded high- $\kappa$  dielectric, conductivity enhancement in the 250 nm width graphene stripes, and superior electrostatic coupling to the gate. Low-voltage actuation alleviates many of the

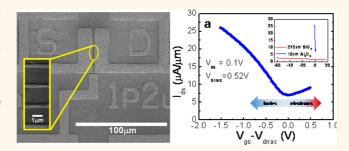

Figure 1. (a) Schematic of device after PMMA transfer of large 6 cm  $\times$  6 cm sheets of APCVD graphene to the Al<sub>2</sub>O<sub>3</sub> dielectric surface, lift-off processing of the Ti/Au contact metal, and finally patterning of the graphene fins in the channel region. It is important to note that there is almost no contrast following PMMA removal, hence the need for large-area graphene over the 100 mm wafer to ensure a statistically sound data set. (b) Scanning electron micrograph (SEM) of a representative device. The inset shows sub-micrometer fin structures of graphene coated with photoresist for clarity.

VOL.7 • NO.7 • 5818-5823 • 2013 A

www.acsnano.org

Figure 2. (a) Raman signatures of graphene films on copper foil and after transfer to the dielectric coated substrate. It was noted that a much higher attractive force existed between graphene and the  $Al_2O_3$  substrate compared to  $SiO_2$  during transfer from the final DI water rinse to the host substrate. Specifically, the graphene sheet could be "repositioned" on the  $SiO_2$  substrate as it glided over the interfacial water layer, whereas the graphene irrevocably "stuck" to the  $Al_2O_3$  surface upon contact. (b) Large-area Raman mapping of the  $I_{2D}/I_G$  intensity ratio indicates continuous and relatively uniform graphene on  $SiO_2$  over very large areas. This criterion was especially important for this study due to the lack of optical contrast between graphene and the thin  $Al_2O_3$  dielectric. (c) Zoomed-in optical image of graphene after transfer to  $SiO_2$  substrate showing wrinkled and folded regions that give rise to anomalies in the Raman map.

Figure 3. (a) Width-normalized  $I_d - V_g$  plot for the back-gated device on a thin Al<sub>2</sub>O<sub>3</sub> dielectric with SiO<sub>2</sub> device shown in the inset. The 0.25  $\mu$ m graphene stripes collectively exhibit an excellent  $I_{ON}/I_{OFF}$  of 3.75. Electron conduction is severely inhibited in these devices due to heavy p-type doping. Typical gate leakage current was <10 nA over the range of  $V_{gs}$  shown with breakdown occurring between 2.5 and 3 V  $V_{gs}$ . The inset shows the dramatic improvement in gate control from adopting the scaled gate dielectric. (b) Histogram of extracted mobility values from top-performing devices across a four-wafer die using three different seed values for regression analysis to simultaneously fit intrinsic carrier concentration, mobility, and contact resistance.

well-known parasitic fringing field issues present in ultrathin body MOSFETs.<sup>23</sup> It is also worth noting that this device architecture is particularly effective in maintaining high mobility due to screening of coulomb and phonon scattering by the high- $\kappa$  dielectric and doublelayer graphene, respectively.<sup>24,25</sup> Patterning the channel into fins in the quarter micrometer regime or smaller has been proposed as a means to enhance double-layer graphene's small band gap while maintaining excellent phonon-limited mobility as opposed to many nanoribbon-based device demonstrations that suffer significant mobility degradation due to edge scattering.<sup>4,26,27</sup> Recent reports have also shown that  $0.5-3 \mu m$  wide graphene stripes experience up to 40% conductivity enhancement at the edges with degradation occurring at smaller widths due to the onset of carrier scattering from the graphene edges.<sup>28</sup> This effect has likely gone unnoticed in other reports of

SMITH ET AL.

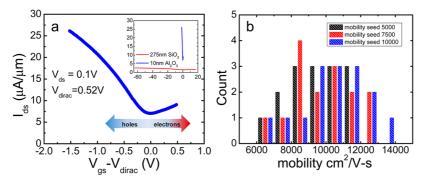

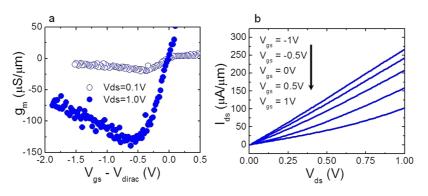

graphene channels patterned into sub-micrometer dimensions because the action of the fringing field to enhance edge conductivity manifests itself most effectively for a dielectric thickness to graphene width ratio  $(t_{ox}/W_{ch}) \ll 1.^{29}$  Hence, our choice of striped channel architecture and dimension coupled with a very thin dielectric is ideally suited to take advantage of edge conductivity enhancement without suffering edge scattering mobility degradation. Figure 3b shows a mobility (mobility data are obtained by overall fitting of  $I_dV_a$  data) histogram from 15 top-performing devices across the wafer. Transfer characteristics at  $V_{ds}$  = 1 V normalized for both channel width and gate overdrive shown in Figure 4 indicate a peak  $g_m/I_{drive}$  ratio that surpasses even the best top-gated devices with seeded deposition ALD films while still maintaining an  $I_{ON}/I_{OFF}$  ratio > 3.<sup>30</sup> As seen in the  $I_dV_d$  plot (Figure 4b), the unique device architecture enables significant

VOL.7 • NO.7 • 5818-5823 • 2013

JAI

www.acsnano.org

Figure 4. (a) Comparison of width-normalized transconductance for  $V_{ds} = 0.1$  and 1 V conditions highlighting the ease of switching the device state at a fraction of gate voltage typically required for back-gated FETs. (b) Output characteristics ( $I_dV_d$ ) indicate the device retains an appreciable  $I_{ON}/I_{OFF}$  ratio for  $V_{ds} = 1$  V. It is important to note that the combined peak  $g_m$  of ~140  $\mu$ S/ $\mu$ m,  $I_d^{sat}$  of >250  $\mu$ A/ $\mu$ m, and  $I_{ON}/I_{OFF}$  ratio of >2.5 outstrip any of the seeded ALD dielectric growth techniques presented in ref 25.

drive current modulation for low 1 V system supply voltage ( $V_{dd}$ ) and implies a room-temperature dc peak gain  $(q_m/q_{ds})$  of 1.3, which is extremely difficult to achieve for FET demonstrations utilizing 1 order of magnitude larger back-gate voltage. A widely accepted model was used to extract effective mobility based on total device resistance.<sup>31,32</sup> The intrinsic (sheet) carrier concentration of  $\sim$ 1.42  $\times$  10<sup>12</sup> cm<sup>-2</sup> and contact resistance that varies between 70% and 80% of the total device resistance (depending upon the back-gate voltage) is guite reasonable and in agreement with the mobility model used. For the Al<sub>2</sub>O<sub>3</sub>-deposited wafer, we examined several gate lengths to ascertain the changing nature of both channel and contact resistance inherent in a backgated device architecture. Extrapolation of transfer length and contact resistivity gave values of 2.25  $\mu$ m and 2.23  $\times$  10<sup>-4</sup>  $\Omega$  · cm<sup>2</sup>, respectively. This large contact resistivity is attributed to a residual photoresist layer present on the graphene/metal interface generated during lift-off processing of the source and drain electrodes since no descum was done prior to metal deposition. Recent reports indicating graphene-metal contact resistance reduction of more than  $1000 \times$ versus untreated surfaces by oxygen plasma removal of residual surface contamination imply that the drive current of our device could be significantly increased by addressing this processing issue.<sup>33</sup> It is important to note that while carrier injection is certainly hampered due to S/D contact resistance, the graphene-dielectric interface suffered no such issues based on our integration scheme and therefore maintains high mobility for the device.

#### CONCLUSIONS

In conclusion, we have detailed a simple integration scheme utilizing a pristine scaled (10 nm) high- $\kappa$  Al<sub>2</sub>O<sub>3</sub> dielectric to fabricate a high-performance APCVD-derived graphene back-gated striped channel FET. The combined  $I_{ON}/I_{OFF}$  ratio of >3 and effective mobility of >11000 cm<sup>2</sup>/V·s indicate the use of pristine ALD dielectrics surpasses deposition methods that require metal/polymer/oxide seeding or surface functionalization typically employed for top-gated transistor architectures. There are several optimizations that can significantly improve the performance of graphene transistors of this type. Specifically, the  $I_{ON}/I_{OFF}$  ratio could be enhanced by more than  $25 \times$  by employing lithographic techniques such as those utilized to generate Intel's 22 nm offering, the Tri-Gate, to pattern graphene stripes in a reliable manufacturable process that maintains excellent line edge roughness to mitigate the edge disorder mobility impact alongside congruent scaling of the gate dielectric to maintain the appropriate  $t_{ox}/W_{ch}$  ratio that preserves edge conductivity enhancement.<sup>34,35</sup> Additionally, reduction of contact resistance to values reported in ref 28 would translate to  $>5\times$  higher drive current. Further reduction of the dielectric thickness below 5 nm is very feasible and would consequently scale the operation voltage for our device to less than 1 V V<sub>dd</sub>. Other integration schemes that utilize buried gate architectures to allow for channel last processing, three-dimensional transfer techniques to increase effective channel width, or substrate engineering to modify residual strain/band gap could also enhance gate control and scalability of high-speed graphene transistors.

#### **METHODS**

tube furnace with customized gas delivery. After surface cleaning in standard solvents, rinsing in deionized water, and drying with nitrogen, the copper foil was loaded into the tube furnace and annealed at atmospheric pressure in an argon/hydrogen

VOL.7 • NO.7 • 5818-5823 • 2013 A

At the beginning, large-area graphene films with low defectivity were synthesized on copper foils ( $25 \,\mu$ m thickness, 99.98% purity from Alfa Aesar) in a commercially available three-zone

(Ar/H<sub>2</sub>) mixture for 30 min at 1050 °C. Following this surface reduction anneal, 500 ppm methane in argon was introduced in place of pure argon for 15–30 min without changing temperature. After growth completion, the sample was pushed out of the hot zone to rapidly quench to room temperature under Ar/H<sub>2</sub> ambient before removing from the furnace. The cooling rate was not measured nor was it specifically controlled to alter the growth. We estimate that the cooling rate is on the order of 300 °C/min from the peak growth temperature of 1000 °C down to 50 °C, whereupon the cooling rate decreases. Raman data were acquired using a 532 nm laser line in a Horiba LabRAM HR unit before and after poly methyl methacrylate (PMMA)-based transfer of the graphene to heavily doped Si wafers coated with either 275 nm thermally grown silicon dioxide (SiO<sub>2</sub>) or 10 nm ALD-deposited aluminum oxide (Al<sub>2</sub>O<sub>3</sub>). The SiO<sub>2</sub> was grown by a dry/wet/dry oxidation sequence in a tube furnace, while Al<sub>2</sub>O<sub>3</sub> was grown via atomic layer deposition using a trimethyl aluminum precursor and H<sub>2</sub>O reactant at 200-250 °C with a deposition rate of  $\sim$ 1 Å/cycle. After solvent removal of PMMA, the wafers were exposed to a nitrogen/hydrogen gas mixture at 450 °C for 10 min to remove any additional PMMA residue and promote photoresist adhesion. Contact mask based liftoff lithography was utilized to pattern 50/200 nm Ti/Au source/drain contacts deposited via e-beam evaporation. Finally, a second mask was used to pattern graphene stripes and thus define the channel regions upon exposure to a short-duration  $O_2/Ar$ reactive ion etch (Figure 1).

Conflict of Interest: The authors declare no competing financial interest.

#### **REFERENCES AND NOTES**

- Geim, A. K. Graphene: Status and Prospects. Science 2009, 324, 1530–1534.

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, 306, 666–669.

- Zhang, Y.; Tang, T.-T.; Girit, C.; Hao, Z.; Martin, M. C.; Zettl, A.; Crommie, M. F.; Shen, Y. R.; Wang, F. Direct Observation of a Widely Tunable Bandgap in Double-Layer Graphene. *Nature* 2009, 459, 820–823.

- Schwierz, F. Graphene Transistors. Nat. Nanotechnol. 2010, 5, 487–496.

- Lin, Y.-M.; Jenkins, K. A.; Valdes-Garcia, A.; Small, J. P.; Farmer, D. B.; Avouris, P. Operation of Graphene Transistors at Gigahertz Frequencies. *Nano Lett.* 2009, *9*, 422–426.

- Lemme, M. C.; Echtermeyer, T. J.; Baus, M.; Kurz, H. A Graphene Field-Effect Device. *IEEE Electron Device Lett.* 2007, 28, 282–284.

- Reina, A.; Jia, Z.; Ho, J.; Nezich, D.; Son, H.; Bulovic, V.; Dresselhaus, M. S.; Kong, J. Large Area, Few-Layer Graphene Films on Arbitrary Substrates by Chemical Vapor Deposition. *Nano Lett.* **2009**, *9*, 30–35.

- Berger, C.; Song, Z.; Li, X.; Wu, X.; Brown, N.; Naud, C.; Mayou, D.; Li, T.; Hass, J.; Marchenkov, A. N.; *et al.* Electronic Confinement and Coherence in Patterned Epitaxial Graphene. *Science* **2006**, *312*, 1191–1196.

- Stankovich, S.; Dikin, D. A.; Piner, R. D.; Kohlhaas, K. A.; Kleinhammes, A.; Jia, Y.; Wu, Y.; Nguyen, S. T.; Ruoff, R. S. Synthesis of Graphene-Based Nanosheets *via* Chemical Reduction of Exfoliated Graphite Oxide. *Carbon* 2007, 45, 1558–1565.

- Moon, J. S.; Curtis, D.; Bui, S.; Hu, M.; Gaskill, D. K.; Tedesco, J. L.; Asbeck, P.; Jernigan, G. G.; VanMil, B. L.; Myers-Ward, R. L.; et al. Top-Gated Epitaxial Graphene FETs on Si-Face SiC Wafers with a Peak Transconductance of 600 mS/mm. *IEEE Electron Device Lett.* **2010**, *31*, 260–262.

- Liao, L.; Bai, J.; Qu, Y.; Huang, Y.; Duan, X. Single-Layer Graphene on Al<sub>2</sub>O<sub>3</sub>/Si Substrate: Better Contrast and Higher Performance of Graphene Transistors. *Nanotechnology* **2010**, *21*, 015705–015709.

- Gao, L.; Ren, W.; Liu, B.; Saito, R.; Wu, Z.-S.; Li, S.; Jiang, C.; Li, F.; Cheng, H.-M. Surface and Interference Coenhanced Raman Scattering of Graphene. ACS Nano 2009, 3, 933–939.

- Badmaev, A.; Che, Y.; Li, Z.; Wang, C.; Zhou, C. Self-Aligned Fabrication of Graphene RF Transistors with T-Shaped Gate. ACS Nano 2012, 6, 3371–3376.

- Li, S.-L.; Miyazaki, H.; Hiura, H.; Liu, C.; Tsukagoshi, K. Enhanced Logic Performance with Semiconducting Bilayer Graphene Channels. ACS Nano 2011, 5, 500–506.

- Lin, Y.-M.; Chiu, H.-S.; Jenkins, K. A.; Farmer, D. B.; Avouris, P.; Valdes-Garcia, A. Dual-Gate Graphene FETs with f<sub>T</sub> of 50 GHz. *IEEE Electron Device Lett.* **2010**, *31*, 68–70.

- Han, S.-J.; Valdes-Garcia, A.; Bol, A. A.; Franklin, A. D.; Farmer, D.; Kratschmer, E.; Jenkins, K. A.; Haensch, W. Graphene Technology with Inverted-T Gate and RF Passives on 200 mm Platform. *IEEE Electron Device Meet.* 2011, 2.2.1–2.2.4.

- Wu, W.; Jauregui, L. A.; Su, Z.; Liu, Z.; Bao, J.; Chen, Y. P.; Yu, Q. Growth of Single Crystal Graphene Arrays by Locally Controlling Nucleation on Polycrystalline Cu Using Chemical Vapor Deposition. *Adv. Mater.* **2011**, 23, 4898–4903.

- Yu, Q.; Jauregui, L. A.; Wu, W.; Colby, R.; Tian, J.; Su, Z.; Cao, H.; Liu, Z.; Pandey, D.; Wei, D.; *et al.* Control and Characterization of Individual Grains and Grain Boundaries in Graphene Grown by Chemical Vapor Deposition. *Nat. Mater.* 2011, *10*, 443–449.

- Wu, W.; Yu, Q.; Peng, P.; Liu, Z.; Bao, J.; Pei, S.-S. Control of Thickness Uniformity and Grain Size in Graphene Films for Transparent Conductive Electrodes. *Nanotechnology* 2012, 23, 035603–035610.

- Wang, Y. Y.; Ni, Z. H.; Yu, T.; Shen, Z. X.; Wang, H. M.; Wu, Y. H.; Chen, W.; Wee, A. T. S. Raman Studies of Monolayer Graphene: The Substrate Effect. *J. Phys. Chem. C* 2008, *112*, 10637–10640.

- Calizo, I.; Bao, W.; Miao, F.; Lau, C. N.; Balandin, A. A. The Effect of Substrates on the Raman Spectrum of Graphene: Graphene-on-Sapphire and Graphene-on-Glass. *Appl. Phys. Lett.* **2007**, *91*, 201904–201906.

- Pirkle, A.; Chan, J.; Venugopal, A.; Hinojos, D.; Magnuson, C. W.; McDonnell, S.; Colombo, L.; Vogel, E. M.; Ruoff, R. S.; Wallace, R. M. The Effect of Chemical Residues on the Physical and Electrical Properties of Chemical Vapor Deposited Graphene Transferred to SiO<sub>2</sub>. *Appl. Phys. Lett.* **2011**, *99*, 122108–122110.

- Ernst, T.; Tinella, C.; Raynaud, C.; Cristoloveanu, S. Fringing Fields in Sub-0.1 μm Fully Depleted SOI MOSFETs: Optimization of the Device Architecture. *Solid-State Electron*. 2002, 46, 373–378.

- Konar, A.; Fang, T.; Jena, D. Effect of High-κ Gate Dielectrics on Charge Transport in Graphene-Based Field Effect Transistors. *Phys. Rev. B* 2010, *82*, 115452–115458.

- Zhu, W.; Perebeinos, V.; Freitag, M.; Avouris, P. Carrier Scattering, Mobilities, and Electrostatic Potential in Monolayer, Double-Layer, and Trilayer Graphene. *Phys. Rev. B* 2009, *80*, 235402–235409.

- Bresciani, M.; Palestri, P.; Esseni, D.; Selmi, L. Simple and Efficient Modeling of the E-k Relationship and Low-Field Mobility In Graphene Nano-Ribbons. *Solid-State Electron.* 2009, 54, 1015–1021.

- Lee, S.; Lee, K.; Zhong, Z. Wafer Scale Homogeneous Double-Layer Graphene Films by Chemical Vapor Deposition. *Nano Lett.* **2010**, *10*, 4702–4707.

- Vasko, F. T.; Zozoulenko, I. V. Conductivity of a Graphene Strip: Width and Gate-Voltage Dependencies. *Appl. Phys. Lett.* 2010, *97*, 092115–092117.

- Venugopal, A.; Chan, J.; Li, X.; Magnuson, C. W.; Kirk, W. P.; Colombo, L.; Ruoff, R. S.; Vogel, E. M. Effective Mobility of Single-Layer Graphene Transistors as a Function of Channel Dimensions. J. Appl. Phys. 2011, 109, 104511– 104515.

- Hollander, M. J.; LaBella, M.; Hughes, Z. R.; Zhu, M.; Trumbull, K. A.; Cavalero, R.; Snyder, D. W.; Wang, X.; Hwang, E.; Datta, S.; et al. Enhanced Transport and Transistor Performance with Oxide Seeded High-κ Gate Dielectrics on Wafer-Scale Epitaxial Graphene. Nano Lett. 2011, 11, 3601–3607.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. Realization of a High Mobility

Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. Appl. Phys. Lett. 2009, 94, 062107-062109.

- 32. Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. L. Current Saturation in Zero-Bandgap, Top-Gated Graphene Field-Effect Transistors. Nat. Nanotechnol. 2008, 3, 654-659.

- 33. Robinson, J. A.; LaBella, M.; Zhu, M.; Hollander, M.; Kasarda, R.; Hughes, Z.; Trumbull, K.; Cavalero, R.; Snyder, D. Contacting Graphene. Appl. Phys. Lett. 2011, 98, 053103-053102.

- 34. Liao, L.; Bai, J.; Cheng, R.; Lin, Y.-C.; Jiang, S.; Huang, Y.; Duan, X. Top-Gated Graphene Nanoribbon Transistors with Ultrathin High-K Dielectrics. Nano Lett. 2010, 10, 1917–1921.

- 35. Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; et al. A 22 nm High Performance and Low-Power CMOS Technology Featuring Fully-Depleted Tri-Gate Transistors, Self-Aligned Contacts and High Density MIM Capacitors. 2012 Symposium of VLSI Technology; VLSI, 2012; pp 131-132.